处理器体系结构

本节简单的介绍处理器的工作方式

由于本章节比较接近底层,因此只大致的说明说了些什么内容

Y86-64指令集体系结构

Y86指令是不存在的,本书的作者受到IA32指令,也就是“x86”的启发,所假想出来的一种处理器体系结构

与 “x86” 相比,Y86指令集的数据类型、指令和寻址方式都要少一些,字节级编码也比较简单。但是它仍然足够完整,能够写一些简单的处理证书的程序,而设计一个Y86处理器要求我们面对许多处理器设计者同样面临的问题。

什么是指令集体系结构?

一个处理器支持的指令和指令的字节编码,称为指令集体系结构(ISA)

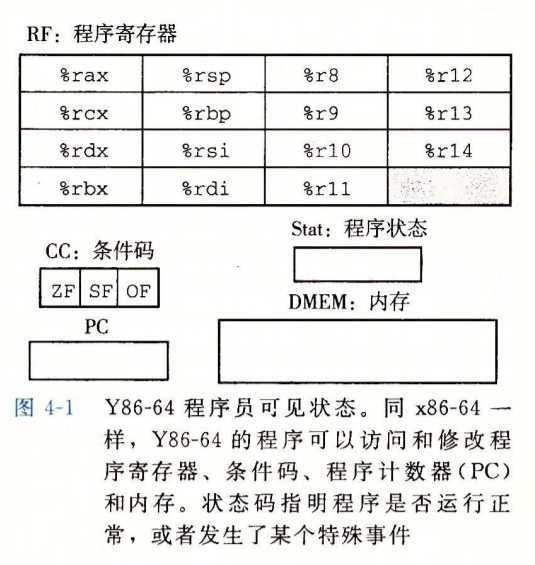

每条指令都会读取和修改处理器状态的某些部分,被称为程序员可见状态

Y86指令集有哪些?

指令如何编码?

如何使用操作数以及操作数如何编码?

状态码Stat有什么用?

以”.”开头的词有什么作用?

pushq %rsp的特殊性?

逻辑设计和硬件控制语言HCL

硬件控制语言HCL有什么用?

什么是逻辑门?

什么是组合电路?

如何使用HCL?

什么是“字”和“情况表达式”?如何用HCL表示?

什么是集合关系?如何用HCL表示?

寄存器和时钟

什么是时钟?有什么作用?

(额外)什么是触发器和锁存器?

什么是时钟寄存器?有什么作用?

时钟寄存器和随机访问存储器的区别?

硬件寄存器和程序寄存器的区别?

Y86-64的顺序(SEQ)实现

处理器顺序执行一条指令会经历哪些阶段?

取指、译码、执行、访存、回写

每个阶段都处理什么问题?

- 取指:获取指令

- 译码:获取指令中的寄存器的值

- 执行:执行各个逻辑单元

- 访存:访存内存,读写内存

- 回写:写入寄存器

具体的各种案例(OPq,rrmovq,irmovq,pushq,popq,jxx,call,ret)

时钟控制下周期执行的处理器上如何实现顺序?

硬件下各位阶段是同时进行的

但是每个阶段产生的结果会作为信号提供给后续阶段使用

直到所有阶段达到一个稳定的状态

时钟上升,所有的结果被写入中

因此,一个时钟周期实现一条指令

哪些结果需要被时钟控制?

需要被后续指令用到的结果:

程序计数器,条件码,寄存器,内存

各阶段如何用HCL表示?

SEQ的缺陷?

流水线的通用原理

如何理解流水线?流水线的优点?

如何从硬件上实现流水线?

流水线的局限?

什么是反馈?

当前指令的结果被后续指令使用

流水线反馈的难题?